超前进位加法器(16位二进制加法器VHDL)

超前进位加法器

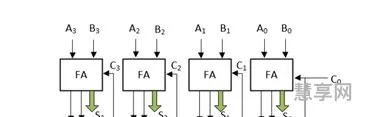

,而无需再从最低位开始向高位逐级传递进位信号了,这就有效的提高了运算速度。采用这种结构形式的加法器为超前进位加法器(Carry-LookaheadAdder)。超前进位加法器设计原理推导:

2超前进位加法器(Carry-Lookahead)设计思想:为了提高运算速度,须减小或消除由于进位信号逐级传递所耗费的时间。由于第i位的进位输入信号

本乘法器采用基4booth编码,输入为两个128位有符号数,输出为256位有符号数。基4的booth编码将两个128位有符号数计算成64个部分积。64个部分积经过一层4-2压缩器得到32个部分积……在经过几层4-2压缩器,最终得到两个部分积,两个部分积进过一个

高密度意味着大量的单元可以被封装到芯片的一个给定的表面区域;也就是说,密度越高,在一个给定尺寸的芯片上可以存储的比特数就越多。

RIGHT/LEFT’选择数据移动方向,当高电平时是右移,低电平时左移。其中的D触发器的输出端都连接着左右两位D触发器的输入端。

16位二进制加法器VHDL

C被称为输入动态指示器(dynamicinputindicator),只有在时钟产生变化的过程中激活,相当于D-gatedLatch中的EN被置HIGH。

一般布尔表达式的域是指该表达式所有变量的集合可以是原码或者反码的形式。例如AB+BC的域是{A、B、C}

).拿原数据和校验位一起Module2除以校验和的代表码。如果传输到接收端以后依然余数为0则没有出错。

SHIFT/LOAD‘故名思意,当为高电平时允许数据位移,当为低电平时允许数据写入。但缺点是不能连续变化,在数据写入时就要暂停移位。

种组合。乘积项之和表达式中至少有一个乘积项为1时,表达式的结果就为1。共有哪几种组合结果可以为1,取决于最小项之和表达式中有几项乘积项。

一位二进制全加器逻辑电路图

def:编码器在其表示数字(如十进制或八进制数字)的一个输入上接受有效电平,并将其转换为编码输出,如BCD或二进制

(synchronous)意味着输出仅在被称为时钟(CLK)的触发输入上的指定点(前沿或后沿)改变状态,该触发输入被指定为控制输入C;即输出的变化与时钟同步地发生。触发器是

的组合,就把C消去。就像消消乐一样。化简的基本目的是,圈尽可能的大,组尽可能的小。卡诺图的数字要连续变化。